## Vertical field-effect transistor based on wave-function extension

A. Sciambi, <sup>1,2</sup> M. Pelliccione, <sup>1,2</sup> M. P. Lilly, <sup>3</sup> S. R. Bank, <sup>4,5</sup> A. C. Gossard, <sup>4</sup> L. N. Pfeiffer, <sup>6</sup> K. W. West, <sup>6</sup> and D. Goldhaber-Gordon<sup>2,7,\*</sup>

<sup>1</sup>Department of Applied Physics, Stanford University, Stanford, California 94305-4045, USA

<sup>2</sup>SIMES, SLAC National Accelerator Laboratory, 2575 Sand Hill Road, Menlo Park, California 94025, USA

<sup>3</sup>Center for Integrated Nanotechnologies, Sandia National Laboratories, Albuquerque, New Mexico 87185, USA

<sup>4</sup>Materials Department, University of California Santa Barbara, Santa Barbara, California 93106, USA

<sup>5</sup>Electrical and Computer Engineering Department, University of Texas at Austin, Austin, Texas 78758, USA

<sup>6</sup>Department of Electrical Engineering, Princeton University, Princeton, New Jersey 08544, USA

<sup>7</sup>Department of Physics, Stanford University, Stanford, California 94305-4045, USA

(Received 19 January 2011; revised manuscript received 21 July 2011; published 18 August 2011)

We demonstrate a mechanism for a dual layer, vertical field-effect transistor, in which nearly depleting one layer will extend its wave function to overlap the other layer and increase tunnel current. We characterize this effect in a specially designed GaAs/AlGaAs device, observing a tunnel current increase of two orders of magnitude at cryogenic temperatures, and we suggest extrapolations of the design to other material systems such as graphene.

DOI: 10.1103/PhysRevB.84.085301 PACS number(s): 73.40.Gk, 73.63.Hs

## I. INTRODUCTION

Quantum transistors, those that rely on quantum mechanical transport processes for operation, have become an important research direction as conventional transistors are hindered by the emergence of those same effects at the nanoscale. In this vein, we present here a mechanism for a vertical field-effect transistor, wherein the adjustable subband energy of a planar quantum well modifies the vertical extent and overlap of its bound wave function with another parallel well. Unlike past quantum transistors that utilize tunnel resonances of aligned subbands<sup>2–4</sup> or single electron levels in quantum dots,<sup>5</sup> this simple design is not sensitive to lateral dimensions and should be operable down to the few-nanometer scale in suitable materials. We call the resulting device the wave-function extension transistor (WET).

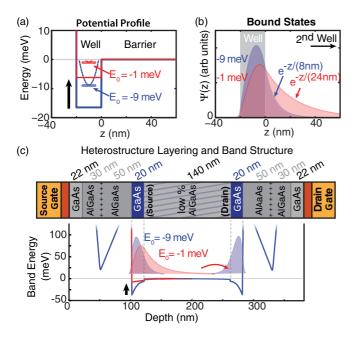

Within a quantum well containing a single subband, the outof-plane momentum and characteristic length scale for barrier penetration for bound electrons is solely determined by the height of the barrier above the bottom of the subband, together with the effective mass, a property of the quantum-well material. In a WET, this barrier normally inhibits tunneling, but its height can be reduced by electrostatically raising the well containing the subband [see Fig. 1(a)]. The rate of exponential decay of the subband wave function into the barrier scales roughly as the square root of the effective barrier height, so reducing the height nearly to zero causes a subband wave function to greatly extend toward the opposing well [see Fig. 1(b)]. Such spreading leads to an increase in wave-function overlap and tunneling. Substantial tuning of wave-function extension and overlap is enabled by (1) having a wide potential barrier separating the two wells to maximize the effect of wave-function decay, and (2) having the barrier height as low as possible to maximize current while ensuring energy levels in the two wells can be separately manipulated. This need for a low and wide barrier means wave-function extension has not been observed in more conventional bilayer quantum well systems with high, narrow barriers, 4,6 strongly-coupled wells,<sup>7</sup> or high interlayer biases.<sup>8</sup> Modulating wave-function overlap has been proposed before for a field-effect tunnel

transistor,<sup>3</sup> but in the context of laterally shaping wave functions using multiple side gates.

In this paper, we simulate and experimentally characterize a proof-of-principle transistor designed according to this scheme: we measure at 4.2 K the tunneling between source and drain layers epitaxially grown in a GaAs/AlGaAs heterostructure [see Fig. 1(c), top], as a function of voltages on top and back gates. In this type of structure, simply bringing a layer near depletion using surface gates should dramatically increase wave-function overlap [see Fig. 1(c), bottom] and the related vertical tunnel conductance, as indeed we observe empirically. This puts the WET into a very small subset of transistors<sup>4</sup> where the conductance is tuned using a gate located outside the channel region, with the source or drain intervening between gate and channel. After characterizing the GaAs/AlGaAs device, we conclude by proposing that a WET operating at room temperature with improved switching characteristics could be constructed based on two parallel layers of graphene. We note here that both the GaAs device and the proposed graphene device are orders of magnitude from the current densities and on-off ratios of commercial transistors. That said, we believe that this mechanism of current-modulation might be useful as new materials and fabrication techniques arise.

## II. THE DEVICE

In order to optimize the tunable tunneling in our GaAs/AlGaAs device, we use self-consistent one-dimensional Schrödinger-Poisson solvers<sup>10</sup> to guide our design of a pair of GaAs/AlGaAs quantum wells separated by a wide, low-energy barrier. We estimate tunnel rates using Bardeen's formalism, <sup>11</sup> which calculates the overlap of wave functions constrained at the opposite sides of the barrier. This yields a tunneling matrix element between wells of equal subband energy that scales roughly as  $T(E_0) \propto \sqrt{|E_0|} e^{-w\sqrt{2m|E_0|}/h}$ , where  $E_0$  is the (negative) energy of the subband edge relative to the barrier, w is the width of the wide barrier, and m is the effective mass of an electron in the barrier. <sup>12</sup>

FIG. 1. (Color online) (a) Potential profile of a shallow barrier next to a rectangular well that is raised so the energy  $E_0$  of its bound subband edge goes from -9 to -1 meV. (b) Simulated wave functions corresponding to the two subband energies, with the raised subband having a greatly extended wave function. (c) WET composition, consisting of a GaAs/AlGaAs heterostructure with gates and dielectric on either side. A self-consistent simulation of the conduction band edge for the structure is shown below,  $^{10}$  with the source gate varying the subband edge of the source quantum well from -9 to -1 meV and extending its associated wave function.

Following optimization, we focus on the structure shown in Fig. 2(c), which we have labeled H1 and use for all measurements unless otherwise noted. The structure contains a pair of two-dimensional (2D) electron layers each residing in a 20-nm-wide GaAs well and separated by a 140-nm-wide Al $_{0.02}$ Ga $_{0.98}$ As barrier. The bilayer system is sandwiched between 80-nm Al $_{0.3}$ Ga $_{0.7}$ As spacers that are delta doped near their midpoint and then between 22-nm GaAs caps. After growth in a molecular beam epitaxy (MBE) system, <sup>13</sup> this heterostructure was found to have source and drain layer densities of  $3.1 \times 10^{11}$  and  $2.9 \times 10^{11}$  cm<sup>-2</sup> with mobilities of  $3 \times 10^6$  and  $1 \times 10^6$  cm<sup>2</sup>/Vs, respectively, all at 4.2 K. The densities are within 10% of their simulated values.

The 2.0% Al barrier, measured precisely during growth with reflection high-energy electron diffraction (RHEED), was found empirically to be the ideal balance between large barrier modulation and large tunnel current. For a 1.0% barrier, we observe that the two wells are not decoupled and for a 3.0% barrier, the minute tunneling is difficult to measure. Determining this optimal percentage from first principles is difficult since the barrier position relative to the Fermi energy can vary by more than 10 meV depending on the exact well shape. Our simulation predicts that the 2.0% barrier is too high (7 meV above  $E_F$ ) to measure the strong gate modulation of tunnel conductance described later. With this disparity in mind, we have adjusted the Al concentration to 0.5% in simulation, and we use this value to demonstrate wave-function extension

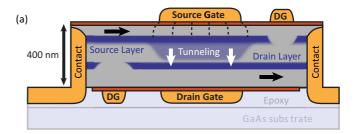

FIG. 2. (Color online) (a) Schematic of WET device (not to scale), with depletion gates (DG) limiting access of the contacts to the tunneling region. (b) Photograph of the finished sample with the GaAs mesa, outlined in purple, supported by epoxy. Hook-shaped protrusions in the mesa are visible where gates overlap, included to ensure continuity during gate deposition over the mesa step.

in Fig. 1(c). This shallower barrier is predicted to be around 1 meV above  $E_F$ .

To determine tunneling between layers, we employ front and back depletion gates<sup>14</sup> [DGs, Fig. 2(a)] to limit access of the sample contacts to only one layer each. In this way, modulation of tunneling by the source and drain gates can be measured by simply applying a bias between the contacts. Backside lithography is accomplished by first fabricating the front side of a sample chip with mesas, contacts, alumina gate dielectric, and gates, and then epoxying that chip face down to a second GaAs substrate. The original substrate is mechanically thinned to 30  $\mu$ m, and then chemically etched to 400 nm using selective removal of etch-stop layers grown into heterostructure. 15 After etching, only the mesa remains of the original substrate, with bare epoxy supporting it as well as features off the mesa like the frontside gates and subsequently added backside gates [see Fig. 2(b)]. With the flipped sample in mind, we refer to the original backside quantum well as the source and the original frontside well as the drain. The source and drain gates areas are 200  $\mu$ m<sup>2</sup>, allowing accurate measurements of tunnel modulation between source and drain by excluding background tunneling or tunneling induced by fringe fields.

The measurement itself is performed with the application of a  $100~\mu\text{V}$  ac excitation driven at 152~Hz between the source and drain layers while a lock-in measures the differential tunneling conductance. We confirmed that the bias between the two layers was set by this ac excitation: the gate dielectric ensures that the measured ac current was always many orders of magnitude larger than any dc gate leakage current. Additionally, we find that interlayer biasing up to tens of mV minimally impacts the densities of the layers, by less than

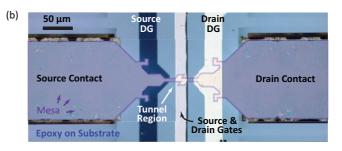

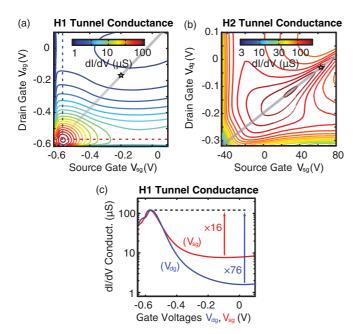

FIG. 3. (Color online) (a) Tunneling conductance as a function of source and drain gate voltages in the main heterostructure H1. Density-matched bilayer resonances (around gray line) are absent, but barrier-modulated tunnel increases along dotted lines are strong. (b) A different heterostructure (H2) with resonant tunneling is shown for comparison. The axes of (a) and (b) are chosen so that both layers are depleted at the lower left corner, with a star added for reference where each layer has a carrier density of  $2 \times 10^{11} \text{ cm}^{-2}$ . (c) Cuts along dotted lines in (a) reveal the large tunnel increases. All data were taken at 4.2 K.

$5 \times 10^8 \ \mathrm{cm^{-2}/mV}$  as determined from Shubnikov-de Haas oscillations.

# III. OBSERVATION OF WAVE-FUNCTION EXTENSION

As expected, tunneling measurements as a function of source and drain gate voltages reveal a pair of conductance ridges [see Fig. 3(a), dotted lines] at 4.2 K associated with near-depletion in the respective layers. Approaching these ridges from the high-density side, the tunnel conductance increase confirms the predicted wave-function extension. These ridges differ from the resonances often seen in tunneling between low-dimensional systems where their energy-momentum dispersions coincide. Such resonances are absent here [see Fig. 3(a), gray line where densities are matched], possibly due to elastic scattering in the interlayer that creates momentum transfer.

For comparison, we show a density-matched tunneling resonance from a similar structure (H2) with a narrower, 70-nm, barrier [see Fig. 3(b)—this structure was thinned only to 10  $\mu$ m and so it required proportionally larger source gate voltages]. In this heterostructure, the near-depletion ridges are also apparent, though mostly obscured by density-matched resonant tunneling (gray line). In a regime lacking interlayer scattering, the WET could operate without impact from energy-momentum constraints if the two layers were set to equal densities and then depleted simultaneously. On Fig. 2(b), this represents moving from the upper right corner along the

gray line toward the tunnel maximum near the plot center. Alternatively, the constraints could be lifted by tunneling from a region comparable in size to the Fermi wavelength ( $\lambda_F$ ), where a large lateral-momentum spread yields access to any momentum state in the other layer. Lifting of momentum constraints in tunneling is why the vertical, tunnel-resonant transistor mentioned earlier<sup>4</sup> fails to operate below a minimum device size.

On the main heterostructure H1, the greatest relative tunnel increase occurs when tuning either gate through the tunnel maximum at  $(V_{\rm sg},V_{\rm dg})=(-0.57~{\rm V},-0.57~{\rm V})$ . The corresponding source and drain gate sweeps, represented by the dotted lines in Fig. 3(a), show tunneling grow by a factor of 16 and 76, respectively [see Fig. 3(c)]. Although the sweeps are not identical, their lineshapes are similar as expected from the symmetry in the heterostructure. Any quantitative difference likely comes from the mechanical and chemical processing that the source layer sees while the drain layer is protected face down in epoxy.

The greater induced tunneling from the drain gate represents a change in effective conductivity from 9 to  $600\,\mathrm{nS}/\mu\mathrm{m}^2$ . The actual tunneling increase is probably larger than the measured conductance enhancement; as a layer is depleted, the growing tunnel conductance is eventually overcome by a low series sheet conductivity. This explains the apparent turnover of gate-modulated tunneling in Fig. 3(c). By independently measuring sheet resistance, we can estimate that the true tunnel conductance increases by at least another order of magnitude. The tunnel signal will not be obscured in this way if one combines smaller-area gates and higher-mobility heterostructures.

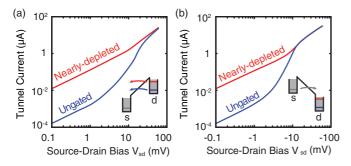

The robustness of wave-function extension is demonstrated by its persistence even when a substantial bias is applied between layers. Here, we choose to focus on the effect of the drain gate rather than the source gate due to the drain gate's greater influence on tunneling. We measure the increase in tunneling from a nearly depleted drain layer compared to an ungated drain layer, as a function of source-drain bias. For a positive source-drain bias, the relative gate-induced increase in current is unchanged for biases up to several mV, and some modulation is visible up to many tens of mV [see Fig. 4(a)]. Low negative biases work similarly [see Fig. 4(b)], though wave-function extension vanishes earlier at high negative bias (10 mV). This is probably because electrons begin to tunnel into the excited states of the drain regardless of its lowest subband energy [schematic: Fig. 4(b), inset]. For positive bias, the drain subband is always the highest accessible level, so it affects tunneling for higher biases [see Fig. 4(a), inset].

## IV. A DEVICE DESIGN FOR ROOM TEMPERATURE

From Fig. 4(a), we can also calculate the transconductance, which peaks at 50 nS/ $\mu$ m<sup>2</sup> at  $V_{\rm sd}=40$  mV at 4.2K. Here, the units of transconductance are per area rather than per length because of the unusual geometry of the transistor. For comparison, metal-oxide-semiconductor field-effect transistors (MOSFETs) can achieve transconductances of 11–30 mS/ $\mu$ m with drives of around 70–200 mV at room temperature. To operate a WET at room temperature with higher transconductances, the effective barrier height needs to be made

FIG. 4. (Color online) (Current modulation by the drain gate as a function of (a) positive and (b) negative source-drain bias. The insets depict a possible explanation for the difference in modulation for large positive and negative biases.

much larger while keeping the absolute barrier low. This can be accomplished by increasing  $E_F$  of the source and drain layers. GaAs heterostructures are limited to Fermi energies of tens of meV. In contrast, graphene, a single atomic layer of graphitic carbon, has been gated to carrier densities  $^{16}$  up to  $3\times10^{13}$  cm $^{-2}$ , which corresponds to  $E_F=0.9$  eV. This is 90 times larger than in our GaAs/AlGaAs heterostructure, with the additional advantage that graphene can be serially deposited and etched so that individual layers can be contacted without depletion gates. Furthermore, graphene is extremely thin, allowing for larger capacitances and transconductances with more closely-spaced gates.

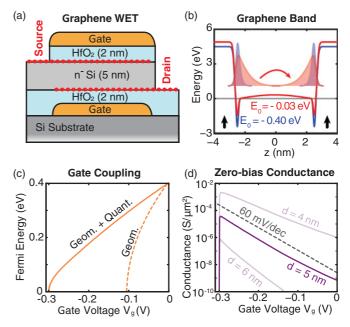

Although graphene field-effect transistors have already been reported with large on-off current ratios at room temperature, 19,20 such devices rely on nanoconstrictions to open band gaps and have been predicted to have low yields for the near future because of difficult device fabrication.<sup>21</sup> A graphene WET would not need precise lateral definition, and would instead depend on its more easily controlled vertical layer structure [see Fig. 5(a)]. We have modeled (but not fabricated) a graphene WET containing two graphene sheets, doped to an easily achievable  $E_F = 0.4$  eV (layer density of  $6 \times 10^{12}$  cm<sup>-2</sup>) and separated by a slightly *n*-doped silicon barrier. The barrier height is chosen so that there exists no excited interlayer subband below ten times room temperature thermal energy (250 meV). The graphene double layer is insulated on each side by a thin layer of high-k dielectric (HfO<sub>2</sub>), and equal voltage is applied to top and back gates to match layer densities and energy-momentum dispersions. (Such a device should also have a high negative differential resistance<sup>4</sup> should the top and bottom gates be differently biased.)

For a 5-nm-wide barrier and 2-nm top and back gate dielectrics, the layer wave functions significantly extend when the subbands are raised [see Fig. 5(b)]. To estimate how gating might accomplish this, the density of states (DOS) of graphene must be considered. Unlike the constant DOS of the 2D GaAs heterostructure, graphene's DOS nominally drops to zero as it is depleted due to its linear dispersion. This introduces problems of quantum capacitance near zero DOS,  $^{22,23}$  which weakens the effect of a gate on  $E_F$  as compared to that expected from the conventional geometric capacitance [see Fig. 5(c)]. (This issue could potentially be alleviated by using bilayer

FIG. 5. (Color online) (a) Schematic of a graphene WET (two graphene layers marked by dotted red lines) and (b) plot of the conduction band with simultaneously varied subband wave functions (shaded). (c) Quantum capacitance, due to a discrete density of states, weakens the effect of the gate, but the device still is able to match 60 mV/decade over several decades (d).

graphene, which has a constant DOS near the K point.) Despite the shrinking DOSs, the tunnel current still increases with negative gate bias, almost to depletion, due to the exponentially increasing tunnel coupling [see Fig. 5(d)].

We have chosen the device parameters such that tunnel modulation is at the room-temperature thermal limit of 60 mV/decade over five decades. For a source-drain bias of 100 mV, where we have offset tunnel gate voltages to account for the bias-induced dispersion mismatch, we find that we should be able to obtain transconductances on the order of 10  $\mu$ S/ $\mu$ m<sup>2</sup> over a 0.3 V gate range. (Note again that transconductance scales with channel area rather than channel width, due to the geometry of the transistor.) If the tunnel barrier is made thicker (6 nm versus 5 nm) the subthreshold slope can beat the thermal limit, provided phonon-assisted processes do not dominate, at the cost of somewhat reduced maximum conductance. We neglect the effect of spatial inhomogeneities in density, <sup>24–26</sup> because the fluctuations are on the order of the thermal energy and because the disorder that gives rise to these fluctuations continues to be reduced with improvements in fabrication technology.<sup>27</sup>

As mentioned previously, the original GaAs/AlGaAs WET is not practical for room-temperature operation, but does have an attractive potential application at low temperature. Using a scanned gate rather than a lithographically patterned gate on a WET structure would allow local tunneling into complex, spatially organized electron phases that sit at buried interfaces and are otherwise locally inaccessible. In this context, we have recently found empirically that the source and drain layers almost completely screen the effect of their respective gates on the opposing 2D layers, that nonequilibrium spectroscopy

can be performed, and that tunneling spatial resolution should be on order of  $\lambda_F$ . <sup>28</sup>

### V. CONCLUSION

In summary, we have used a bilayer GaAs/AlGaAs heterostructure to demonstrate the soundness of the simple WET principle. The behavior of the tunnel modulation as a function of gate voltage and bias is understood qualitatively, and should permit the creation of WETs with useful specifications, using other materials. Furthermore, the GaAs/AlGaAs heterostructure as grown could serve as a tool for probing interesting physics. Again, although the WET design is not yet fully competitive with conventional transistors, wave-function extension combined with new materials and fabrication techniques could lead to a new class of quantum transistors based on vertical transport in heterostructures.

### **ACKNOWLEDGMENTS**

We thank C. X. Liu for theoretical discussions. This work is supported by DOE-BES, DMS&E at SLAC (DE-AC02-76SF00515), with the original concept developed under the Center for Probing the Nanoscale (NSF NSEC Grant No. 0425897) and a Mel Schwartz Fellowship from the Stanford Physics Department. This work was performed, in part, at the Center for Integrated Nanotechnologies, a DOE-BES user facility at Sandia National Labs (DE-AC04-94AL85000). The work at Princeton was partially funded by the Gordon and Betty Moore Foundation as well as the National Science Foundation MRSEC Program through the Princeton Center for Complex Materials (DMR-0819860). A.S. acknowledges support from NSF, and M.P. from the Hertz Foundation, NSF, and Stanford. D.G.-G. recognizes support from the David and Lucile Packard Foundation.

<sup>\*</sup>Corresponding author: goldhaber-gordon@stanford.edu

<sup>&</sup>lt;sup>1</sup>Semiconductor Industry Association., The International Technology Roadmap for Semiconductors, 2009 edition. SEMATECH: Austin, TX [http://www.itrs.net/Links/2005ITRS/ExecSum2005.pdf].

<sup>&</sup>lt;sup>2</sup>V. R. Kolagunta, D. B. Janes, G. L. Chen, K. J. Webb, M. R. Melloch, and C. Youtsey, Appl. Phys. Lett. **69**, 374 (1996).

<sup>&</sup>lt;sup>3</sup>J. B. Khurgin and D. Yang, J. Appl. Phys. **85**, 3218 (1998).

<sup>&</sup>lt;sup>4</sup>J. A. Simmons, M. A. Blount, J. S. Moon, S. K. Lyo, W. E. Baca, J. R. Wendt, J. L. Reno, and M. J. Hafich, J. Appl. Phys. **84**, 5626 (1998).

<sup>&</sup>lt;sup>5</sup>M. A. Kastner, Rev. Mod. Phys. **64**, 849 (1992).

<sup>&</sup>lt;sup>6</sup>J. P. Eisenstein, L. N. Pfeiffer, and K. W. West, Phys. Rev. Lett. **69**, 3804 (1992).

<sup>&</sup>lt;sup>7</sup>H. C. Manoharan, Y. W. Suen, M. B. Santos, and M. Shayegan, Phys. Rev. Lett. **77**, 1813 (1996).

$<sup>^8</sup> M.$  Heiblum and M. V. Fischetti, IBM J. Res. Dev.  ${\bf 34}, 530 \ (1990).$

<sup>&</sup>lt;sup>9</sup>R. J. Baker, *CMOS Circuit Design, Layout, and Simulation*, 3rd ed. (Wiley IEEE Press, New York, NY, 2010).

<sup>&</sup>lt;sup>10</sup>Simulations used code by G. L. Snider, University of Notre Dame, and by C. X. Liu, Tsinghua University.

<sup>&</sup>lt;sup>11</sup>J. Bardeen, Phys. Rev. Lett. **6**, 57 (1961).

<sup>&</sup>lt;sup>12</sup>R. Clerc, A. Spinelli, G. Ghibaudo, and G. Pananakakis, J. Appl. Phys. **91**, 1400 (2002).

<sup>&</sup>lt;sup>13</sup>Heterostructure H1 and H2 were grown by L.N.P. and K.W.W.

<sup>&</sup>lt;sup>14</sup>J. P. Eisenstein, L. N. Pfeiffer, and K. W. West, Appl. Phys. Lett. 57, 2324 (1990).

<sup>&</sup>lt;sup>15</sup>M. V. Weckwerth, J. A. Simmons, N. E. Harff, M. E. Sherwin, M. A. Blount, W. E. Baca, and H. C. Chui, Superlattices Microstruct. 20, 561 (1996).

<sup>&</sup>lt;sup>16</sup>K. S. Novoselov, A. K. Geim, S. V. Morozov, D. Jiang, Y. Zhang, S. V. Dubonos, I. V. Grigorieva, and A. A. Firsov, Science 306, 666 (2004).

$<sup>^{17}</sup>$ Density up to  $4 \times 10^{14}$  cm $^{-2}$  has been achieved in graphene using electrolytic gates, though this approach would not be viable for practical devices. D. K. Efetov and P. Kim, Phys. Rev. Lett. **105**, 256805 (2010).

<sup>&</sup>lt;sup>18</sup>S. Kim, I. Jo, J. Nah, Z. Yao, S. K. Banerjee, E. Tutuc, Phys. Rev. B 83, 161401(R) (2011).

<sup>&</sup>lt;sup>19</sup>M. Y. Han, B. Özyilmaz, Y. Zhang, and P. Kim, Phys. Rev. Lett. 98, 206805 (2007).

<sup>&</sup>lt;sup>20</sup>X. Li, X. Wang, L. Zhang, S. Lee, and H. Dai, Science 319, 1229 (2008).

<sup>&</sup>lt;sup>21</sup>A. K. Geim, Science **324**, 1530 (2009).

<sup>&</sup>lt;sup>22</sup>L. A. Ponomarenko, R. Yang, R. V. Gorbachev, P. Blake, A. S. Mayorov, K. S. Novoselov, M. I. Katsnelson, and A. K. Geim, Phys. Rev. Lett. **105**, 136801 (2010).

<sup>&</sup>lt;sup>23</sup>A. Hazeghi, J. A. Sulpizio, G. Diankov, D. Goldhaber-Gordon, and H. S. Philip Wong, Rev. Sci. Instrum. 82, 053904 (2011).

<sup>&</sup>lt;sup>24</sup>J. Martin, N. Akerman, G. Ulbricht, T. Lohmann, J. H. Smetr, K. von Klitzing, and A. Yacoby, Nat. Phys. 4, 144 (2008).

<sup>&</sup>lt;sup>25</sup>Y. Zhang, V. W. Brar, C. Girit, A. Zettl, and M. F. Crommie, Nat. Phys. 5, 722 (2009).

<sup>&</sup>lt;sup>26</sup>E. Rossi and S. Das Sarma, Phys. Rev. Lett. **101**, 166803 (2008).

<sup>&</sup>lt;sup>27</sup>C. R. Dean, A. F. Young, I. Meric, C. Lee, L. Wang, S. Sorgenfrei, K. Watanabe, T. Taniguchi, P. Kim, K. L. Shepard, and J. Hone, Nat. Nano. 5, 722 (2010).

<sup>&</sup>lt;sup>28</sup>A. Sciambi, M. Pelliccione, S. R. Bank, A. C. Gossard, and D. Goldhaber-Gordon, Appl. Phys. Lett. 97, 132103 (2010).